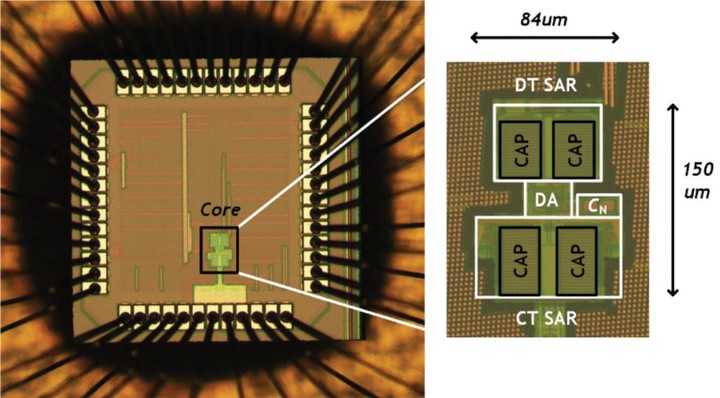

3.4 A 0.01mm2 25µW 2MS/s 74dB-SNDR Continuous-Time Pipelined-SAR ADC with 120fF Input Capacitor

Abstract

The kT/C noise poses a fundamental SNR limit for discrete-time (DT) ADCs with front-end sampling operations. To achieve a high resolution, the sampling capacitor needs to be sufficiently large (e.g., 3pF for 80dB SNR assuming 2V pp swing) and it has to be quadrupled for every 1b increase in the resolution. A large sampling capacitor poses critical challenges for both the ADC input buffer and the reference buffer (Fig. 3.4.1). To meet the stringent linearity requirement of high-resolution ADCs, these buffers consume a significant amount of power, which can be comparable or even higher than the ADC itself. In addition, a large capacitor makes it difficult to design the ADC front-end S/H circuit, leading to considerable power/area costs and increased design complexity.