A 74.5-dB Dynamic Range 10-MHz BW CT-ΔΣ ADC With Distributed-Input VCO and Embedded Capacitive-π Network in 40-nm CMOS

Abstract

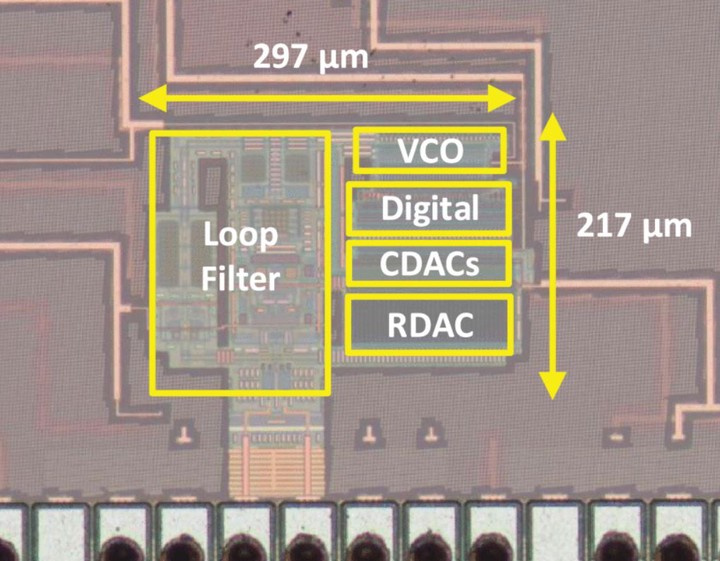

This work introduces a second-order voltage-controlled oscillator (VCO)-based continuous-time delta-sigma modulator (CTDSM) that incorporates a distributed-input VCO as the second-stage integrator and quantizer. The distributed-input VCO topology virtually eliminates the VCO’s voltage-to-frequency (V-F) parasitic pole. One of the key ideas of this article is to demonstrate the use of a capacitive-π network in the modulator’s loop filter to break the constraint between the size of the modulator’s inner capacitive digital-to-analog converter (DAC) and the factor by which the front-end Gm-C integrator is impedance scaled. This, in turn, helps to significantly reduce both analog and digital powers. The prototype chip has been fabricated in a 40-nm CMOS process. Despite not using any DAC calibration or explicit dynamic element matching (DEM) circuits, the worst case spurious-free dynamic range (SFDR) is -82 dBc across the signal bandwidth. The fabricated CTDSM achieves a 71.8-dB signal-to-noise-and-distortion ratio (SNDR) and a 74.5-dB dynamic range (DR) in a 10-MHz bandwidth at 655 MS/s, yielding an SNDR-based Walden figure of merit (FoM) of 45.6 fJ/step, an SNDR-based Schreier FoM of 167.2 dB, and a DR-based Schreier FoM of 169.9 dB.