A Fully Passive Compressive Sensing SAR ADC for Low-Power Wireless Sensors

Abstract

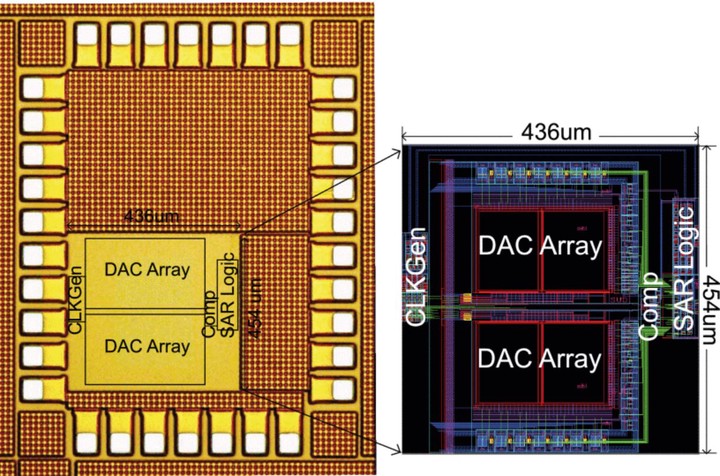

The compressive sensing (CS) theory states that the sparsity of a signal can be exploited to reduce the analog-to-digital converter (ADC) conversion rate and save power. However, most previous CS frameworks require dedicated analog CS encoders built by power-hungry active amplifiers, which limit the overall power saving. Differently, this paper proposes a fully passive switched-capacitor-based CS framework that directly embeds CS into a successive-approximation-register (SAR) ADC. The proposed CS-SAR ADC can operate in two modes: the Nyquist mode and the CS mode. In the CS mode, the CS-SAR ADC quantizes the input once every four-time sampling, reducing the conversion rate and the circuit power by four times compared to the Nyquist mode. A prototype chip is fabricated in a 0.13-μm CMOS process. At 0.8 V and 1 MS/s, the chip consumes 19.2 μW in the Nyquist mode and 5 μW in the CS mode. Discrete-tone signals are converted and reconstructed with a peak signal-to-noise plus distortion ratio (SNDR) of 61 dB and maximum bandwidth occupancy of 8.2%. Speech signals are also used to demonstrate the capability of the chip to compressively sense real-world signals. Compared to prior CS works, it improves the post-reconstruction SNDR by 18 dB and the energy efficiency by 13 times.