A Pipeline SAR ADC With Second-Order Interstage Gain Error Shaping

Abstract

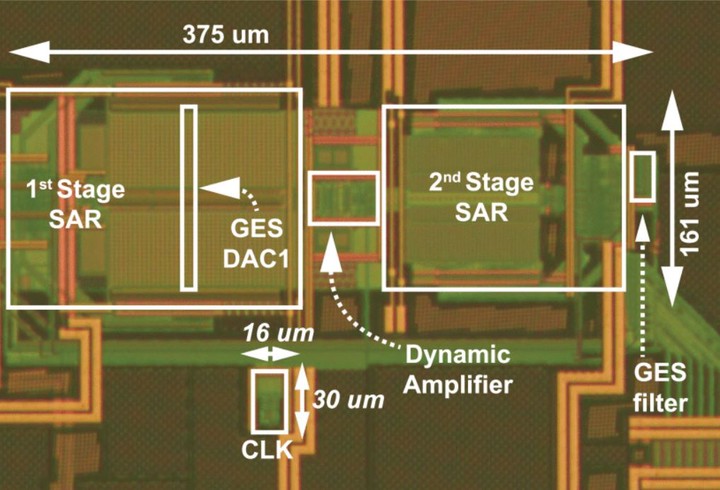

This article presents an interstage gain error shaping (GES) technique that can substantially suppress the in-band quantization leakage error caused by the interstage gain error in pipeline analog-to-digital converters (ADCs). It works for both closed-loop and open-loop amplification. It does not require extra clock phases, long convergence time or an interruption of the digitization, incur large power or area overhead, or pose a constraint on the input signal. A prototype ADC equipped with the proposed second-order GES technique in 40-nm CMOS achieves a 75.8-dB signal-to-noiseand-distortion ratio (SNDR) over 12.5-MHz bandwidth while operating at 100 MS/s and consuming 1.54 mW. It achieves 174.9-dB Schreier figure of merit (FoM). The GES-related hardware only occupies less than 2% of the total active area.