A 7-bit 900-MS/s 2-Then-3-bit/cycle SAR ADC With Background Offset Calibration

Abstract

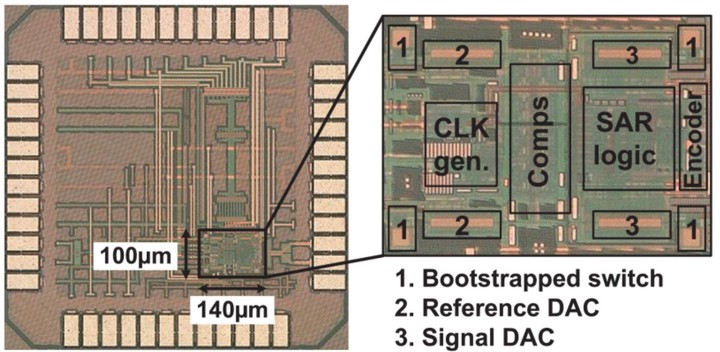

This article presents a 7-bit 900-MS/s multi-bit/cycle successive approximation register (SAR) analog-to-digital converter (ADC) with background offset calibration. Unlike prior works that adopt either four capacitive DACs (CDACs) or interpolated resistive DAC to enable 3-bit/cycle operation, the proposed technique uses only two CDACs to realize the same functionality. The number of CDACs is reduced by embedding gain inside the two-path comparators, resulting in reduced power, area, and input loading. In addition, the built-in redundancy relaxes the accuracy requirements for DAC settling and comparators. On-chip background offset calibration with narrow pulse charge sharing is used to further improve the ADC linearity. The prototype fabricated in 40-nm LP CMOS achieves an SNDR of 39.7 dB at Nyquist input and consumes 2.6 mW including on-chip calibration, leading to a Walden FoM of 36.6 fJ/conversion-step.