A Fully Dynamic Low-Power Wideband Time-Interleaved Noise-Shaping SAR ADC

Abstract

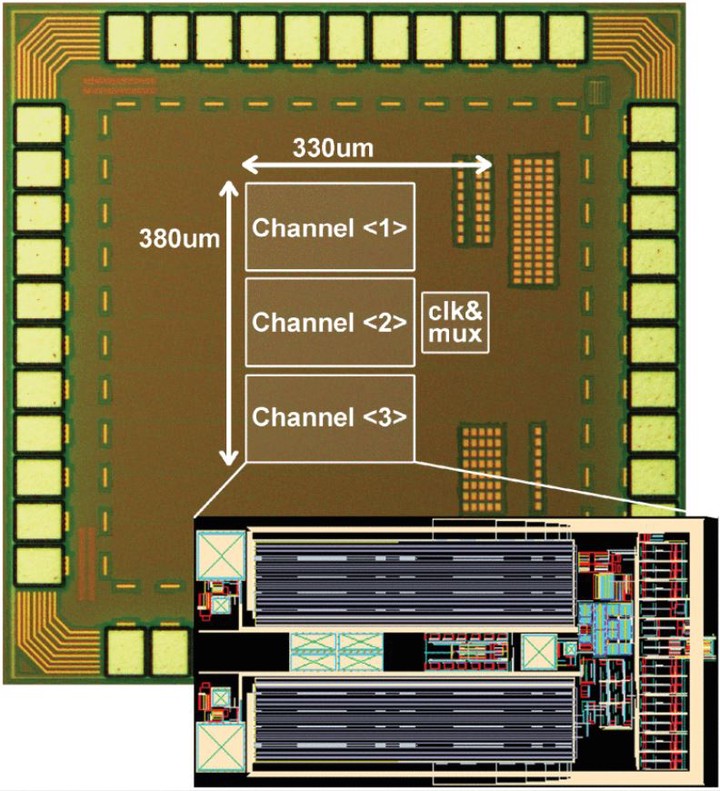

This article proposes a fully dynamic, low-power, wideband, time-interleaved (TI), noise-shaping (NS) successive-approximation-register (SAR) analog-to-digital converter (ADC) based on the cascade of integrators with feedforward (CIFF) architecture. Both the interleaving operation and the loop filter are implemented by using the fully passive switched-capacitor circuits. The feedforward summation is realized by a multi-path dynamic comparator. The overall noise transfer function (NTF) is highly robust against process, voltage, and temperature (PVT) variations since the NTF is determined by device ratios. This allows the NTF zeros to be close to 1, with a good NS effect. Compared with a recently published TI NS SAR based on the error-feedback (EF) architecture, this work does not need a static amplifier, thus leading to the fully dynamic operation. Meanwhile, it eliminates the dependence of NTF on the PVT-sensitive amplifier gain. Implemented in a 40-nm CMOS process, the prototype ADC achieves an SNDR of 69.1 dB, a bandwidth of 50 MHz, and a power consumption of 8.5 mW under a 1.1-V supply, leading to a Walden FoM of 36.3 fJ/conv.-step.