A 13-ENOB 2nd-order noise-shaping SAR ADC realizing optimized NTF zeros using an error-feedback structure

摘要

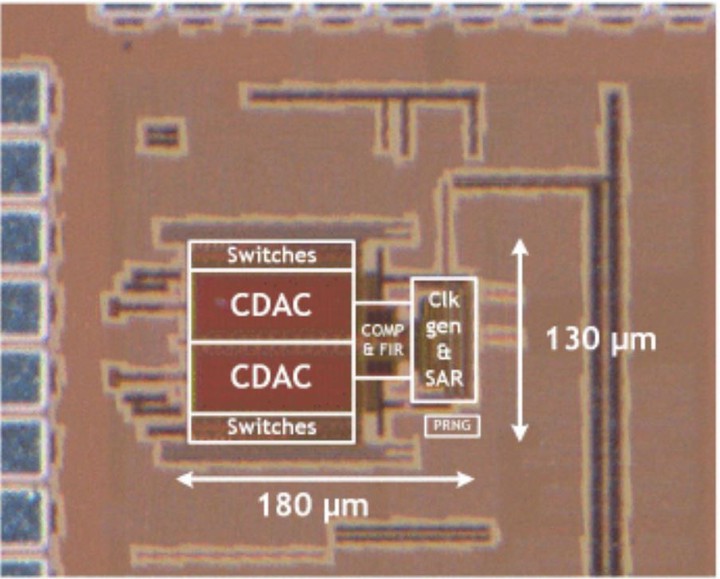

The noise-shaping (NS) SAR ADC is an emerging hybrid architecture that achieves high resolution and power-efficiency simultaneously by combining the merits of the SAR ADC and the AIADC, making it attractive to sensor readout and healthcare applications. To implement NS, most prior works adopted the classic cascaded integrator feed-forward (CIFF) structure for noise filtering [1-5]. Opamp-based integrators were used in [1-3] to achieve a relatively sharp noise transfer function (NTF), but at the cost of power and scaling friendliness. Reference [4] demonstrated 2 nd -order NS using fully passive switched-capacitor (SC) integrators, but has limited NS and thermal noise performance. Reference [5] combines passive SC filters with a dynamic amplifier (D-amp) to achieve good noise and power, but is vulnerable to process-voltage-temperature (PVT) variations. In addition, no prior NS SAR has realized complex NTF zeros for optimum NS. This presents a need for an NS SAR ADC that can combine optimized NTF, power efficiency and PVT robustness. To overcome the limitations of existing work, instead of adopting the CIFF structure, this paper presents a 2 nd -order NS SAR ADC using an error-feedback (EF) structure. It highlights the capability of realizing optimized complex NTF zeros by simply using charge sharing summation, a passive SC FIR and a comparator-reused dynamic amplifier with PVT tracking. This work achieves sharp NS performance while maintaining both hardware and power efficiency merits of the NS SAR with improved robustness. The prototype chip, fabricated in 40nm CMOS, achieves a 79dB SNDR at an OSR of 8 using a 9b SAR, resulting in a peak Schreier FoM of 178dB.