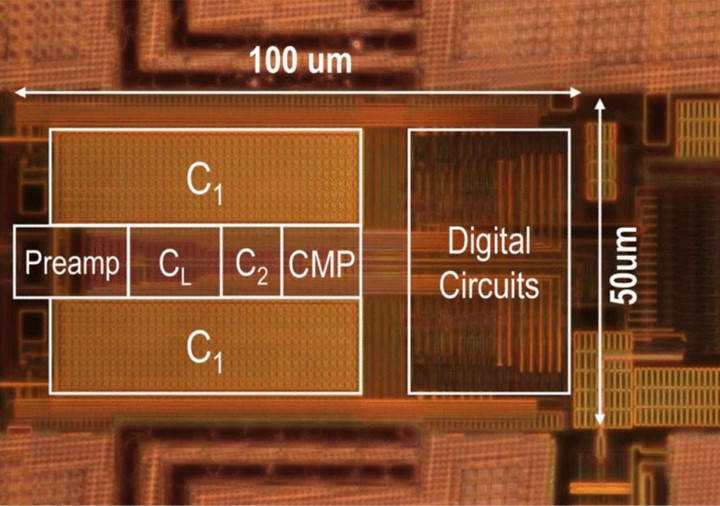

16.5 A 13b 0.005mm2 40MS/s SAR ADC with kT/C Noise Cancellation

摘要

As with any ADC with a front-end S/H, the SAR ADC suffers from a fundamental SNR challenge: its sampling kT/C noise. To satisfy the SNR requirement, the input capacitor has to be sufficiently large (e.g. 3pF for a 13b ADC with 2V pp swing). This, however, makes it very costly to design the ADC input driver and the reference buffer. The input driver and the reference buffer are the bottleneck nowadays. Their power, area, and design complexity can be an order of magnitude higher than the SAR ADC core.

类型

出版物

2020 IEEE International Solid- State Circuits Conference - (ISSCC)