An Energy-Efficient Hybrid SAR-VCO ΔΣ Capacitance-to-Digital Converter in 40-nm CMOS

摘要

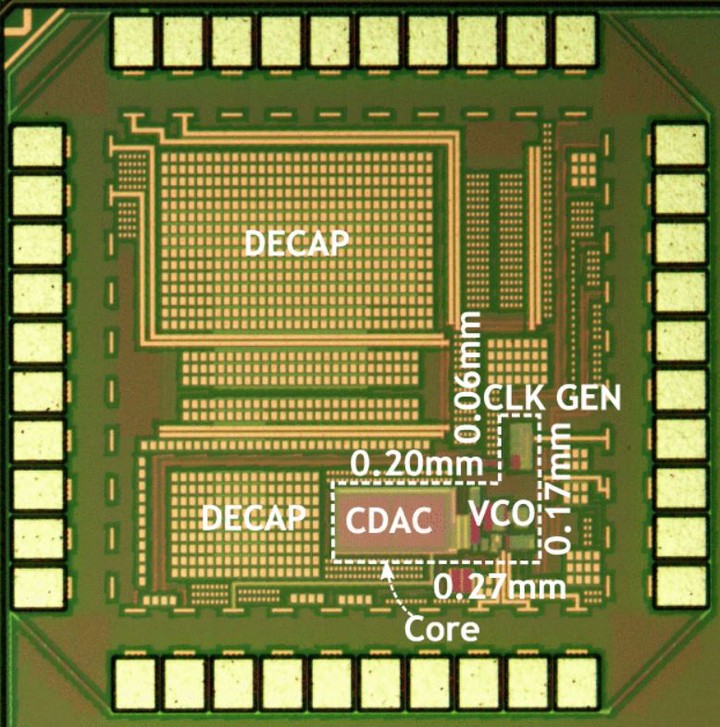

This paper presents a highly digital, 0-1 MASH capacitance-to-digital converter (CDC). The CDC works by sampling a reference voltage on the sensing capacitor and then quantizing the charge stored in it by a 9-bit successive approximation register analog-to-digital converter. The residue is fed to a ring voltage-controlled oscillator (VCO) ΔΣ and quantized in time domain. The outputs from the two stages are combined to produce a quantized output with the first-order noise shaping. The proposed two-stage architecture reduces the impact of the VCO’s nonlinearity. A digital calibration technique is used to track the VCO’s gain across process, voltage, and temperature. The absence of any operational amplifier and low oversampling ratio for the VCO results in high energy efficiency. A prototype CDC in a 40-nm CMOS process achieves a 64.2-dB SNR while operating from a 1-V supply and using a sampling frequency of 3 MHz. The prototype achieves a CDC figure of merit of 55 fJ/conversion-step.