A 6-bit 0.81-mW 700-MS/s SAR ADC With Sparkle-Code Correction, Resolution Enhancement, and Background Window Width Calibration

摘要

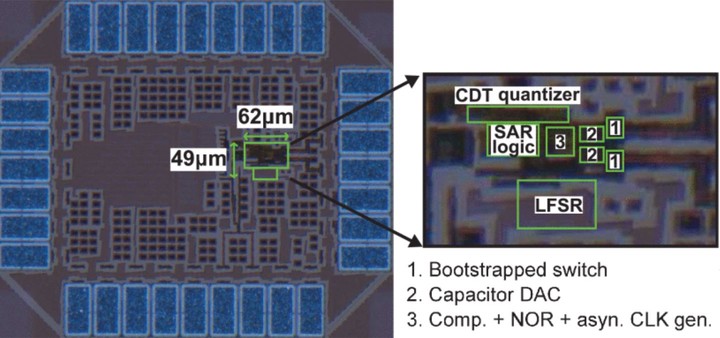

This paper presents a 6-bit high-speed successive approximation register analog-to-digital converter (ADC) with sparkle-code correction. By quantizing the comparator decision time (CDT), the sparkle codes are identified and corrected, reducing the error rate from 10 -4 to below 10 -9 . Furthermore, CDT quantization enables 1-bit increase in the ADC resolution by setting the detection boundary to be ±0.25 LSB. Thus, only five comparison cycles are needed to reach 6 bits, leading to an increased ADC speed. A novel dither-based background calibration technique is devised to accurately control the CDT detection window size and ensure process, temperature, and voltage robustness. A prototype ADC in 40-nm CMOS achieves 35.3-dB signal-to-noise/distortion ratio (SNDR) and consumes 0.81 mW while sampling at 700 MS/s.