A 13-ENOB Second-Order Noise-Shaping SAR ADC Realizing Optimized NTF Zeros Using the Error-Feedback Structure

摘要

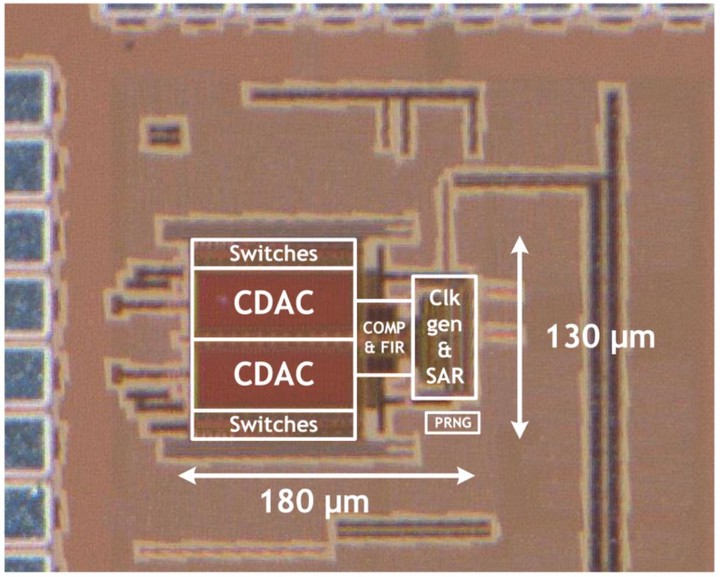

The noise-shaping successive approximation register (NS-SAR) analog-to-digital converter (ADC) is an emerging hybrid architecture that achieves high resolution and power efficiency simultaneously by combining the merits of the SAR ADC and the ΔΣ ADC. Most prior works adopting the cascaded integrator feed-forward (CIFF) structure demonstrate inefficiency in realizing optimized noise transfer function (NTF). This paper presents a second-order NS-SAR ADC employing the error-feedback (EF) structure to realize complex NTF zeros for noise-shaping enhancement with the minimum modification to a standard SAR. It implements a low-power scaling-friendly EF path by using a passive finite impulse response (FIR) and a comparator-reused dynamic amplifier with process-voltagetemperature (PVT) tracking background calibration. Fabricated in 40-nm CMOS, the prototype chip consumes 84 μW when operating at 10 MS/s. The NS-SAR achieves peak Schreier FoM of 178 dB with 79-dB signal to noise and distortion ratio (SNDR) at an oversampling ratio (OSR) of 8.