A Two-Step ADC With a Continuous-Time SAR-Based First Stage

摘要

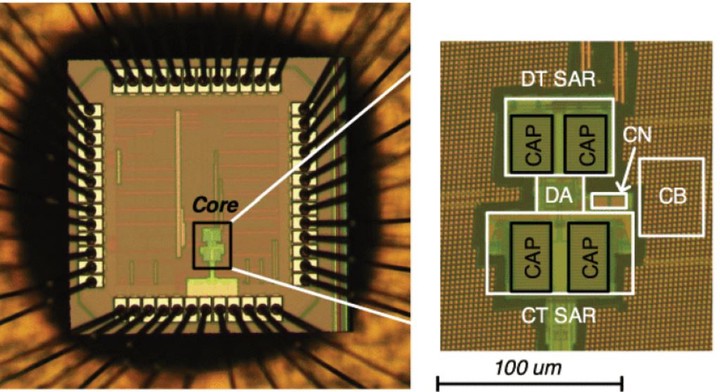

This article presents a two-step analog-to-digital converter (ADC) that operates its first-stage successive approximation register (SAR) ADC in the continuous-time (CT) domain. It avoids the front-end sample-and-hold (S/H) circuit and its associated sampling noise. Hence, the proposed ADC allows the input capacitor size to be substantially reduced without incurring large sampling noise penalty. With input ac coupling, the first-stage CT-SAR can simultaneously perform input tracking and SAR quantization. Its conversion error is minimized by accelerating the SAR speed and providing redundancy. A floating-inverter-based (FIB) dynamic amplifier (DA) is used as the inter-stage amplifier and acts as a low-pass filter for the first-stage residue. To verify the proposed techniques, a 13-bit prototype ADC is built in 40-nm CMOS process. Its input capacitor is only 120 fF, which is over 20 times smaller than what would be needed in a classic Nyquist ADC with the S/H circuit. Operating at 2 MS/s, it achieves 72-dB signal-to-noise-and-distortion-ratio (SNDR) at the Nyquist rate while consuming only 25 μW of power and 0.01 mm 2 of area.