A Fractional- N PLL With Space–Time Averaging for Quantization Noise Reduction

摘要

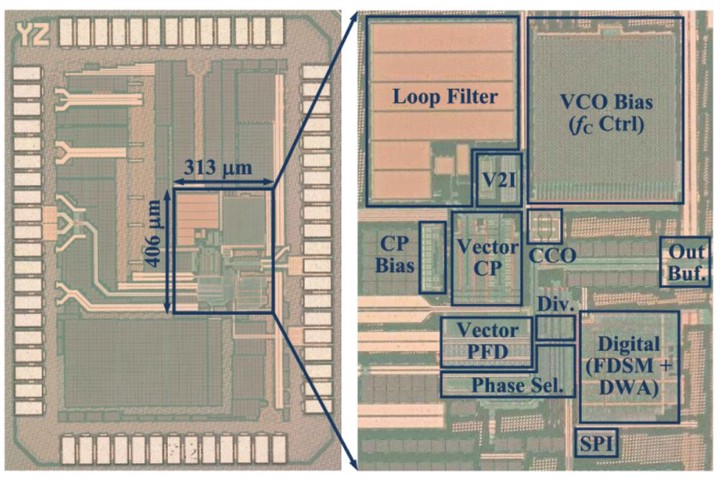

This article presents a space-time averaging technique that can realize instantaneous fractional frequency division, and thus, can significantly reduce the quantization error in a fractional-N phase-locked loop (PLL). Spatial averaging can be achieved by using an array of dividers running in parallel. Their different division ratios are generated by using a fractional ΔΣ modulator (DSM) and a dynamic element matching (DEM) block. To reduce the divider power, this article also proposes a way to achieve spatial averaging using only one divider and phase selection. A prototype 2.4-GHz fractional-N PLL is implemented in a 40-nm CMOS process. Measurement results show that the proposed technique reduces the phase noise by 10 and 21 dB at the 1and 10-MHz offset, respectively, leading to a reduction of the integrated rms jitter from 9.55 to 2.26 ps.