A 13-bit 0.005-mm2 40-MS/s SAR ADC With kT/C Noise Cancellation

摘要

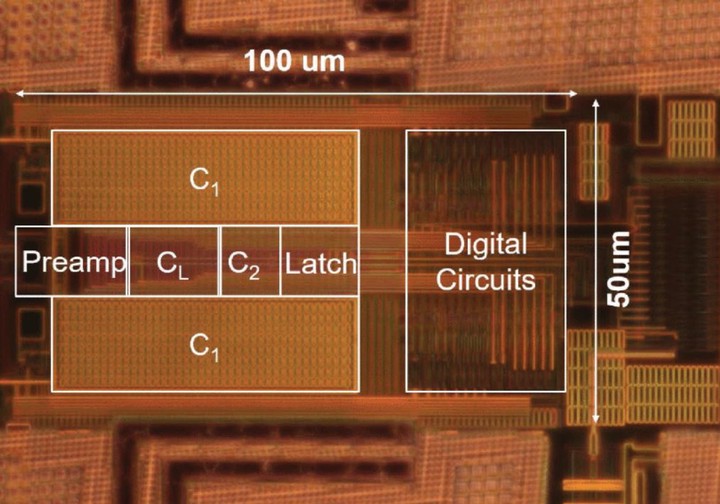

As any analog-to-digital converter (ADC) with a front-end sample-and-hold (S/H) circuit, successive approximation register (SAR) ADC suffers from a fundamental signal-to-noise ratio (SNR) challenge: its sampling kT/C noise. To satisfy the SNR requirement, the input capacitor size has to be sufficiently large, leading to a great burden for the design of the ADC input driver and reference buffer. This article presents an SAR ADC with a kT/C noise-cancellation technique. It enables the substantial reduction of ADC input capacitor size but without the large kT/C noise penalty. It greatly relaxes the requirement for ADC input driver and reference buffer. Built in 40-nm CMOS, a prototype 13-bit ADC has only 240-fF input capacitance and occupies a small area of 0.005 mm 2 . Operating at 40 MS/s, it achieves a 69-dB signal-to-noise-and-distortion ratio (SNDR) across the Nyquist frequency band while consuming 591 μW of power.